cout(z)) Ĭarry Select Adder Simulation Result is as follows:ġ6 bit Carry Select Adder Testbench ////TestbenchĬarry_select_adder_16bit uut(.a(a).

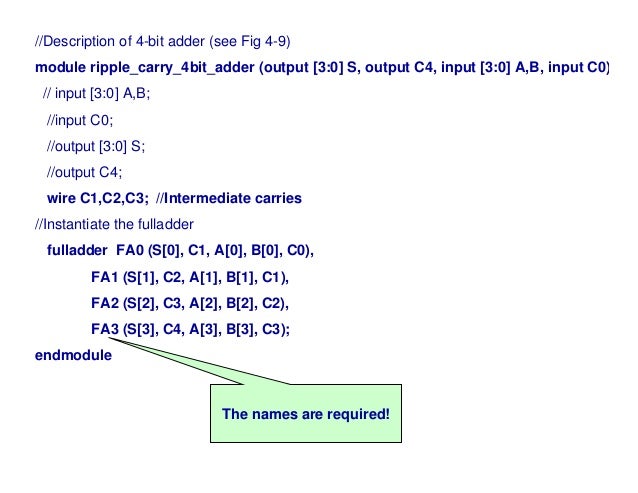

Module ripple_carry_4_bit(a, b, cin, sum, cout) Module carry_select_adder_4bit_slice(a, b, cin, sum, cout) Module carry_select_adder_16bit(a, b, cin, sum, cout) Ĭarry_select_adder_4bit_slice csa_slice1(Ĭarry_select_adder_4bit_slice csa_slice2(Ĭarry_select_adder_4bit_slice csa_slice3( The Verilog Code for 16-bit Carry Select Adder is given below- `timescale 1ns / 1ns module clatb () // test the 8-bit cla // inputs reg 7:0 a reg 7:0 b reg carryin // outputs wire carryout wire 7:0 sum wire pg wire gg // instantiate the 8-bit cla cla8bit cla8bitdut (. Each full adder carry output is connected as an input carry to the next stage full adder.

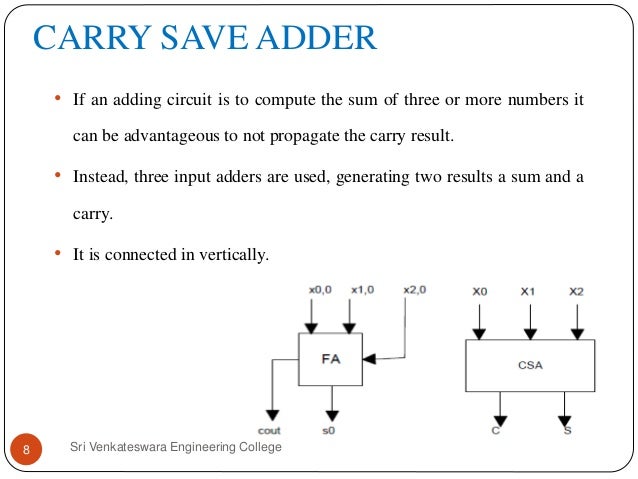

posts to get insight about different adders.īasic structure of 4-bit Carry Select Adder is shown below. 8-bit Ripple Carry Adder It consists of 8 full adders which are connected in cascaded form. Also, you can go through Ripple Carry Adder, Carry Skip Adder, Carry Look-ahead Adder etc. The carry select adder is simple but rather fast. For more information about carry select adder you can refer to this wikipedia article. A carry select adder is a particular way to implement an adder, which is a logic element that computes the (n+1)-bit sum of two n-bit numbers.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed